- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

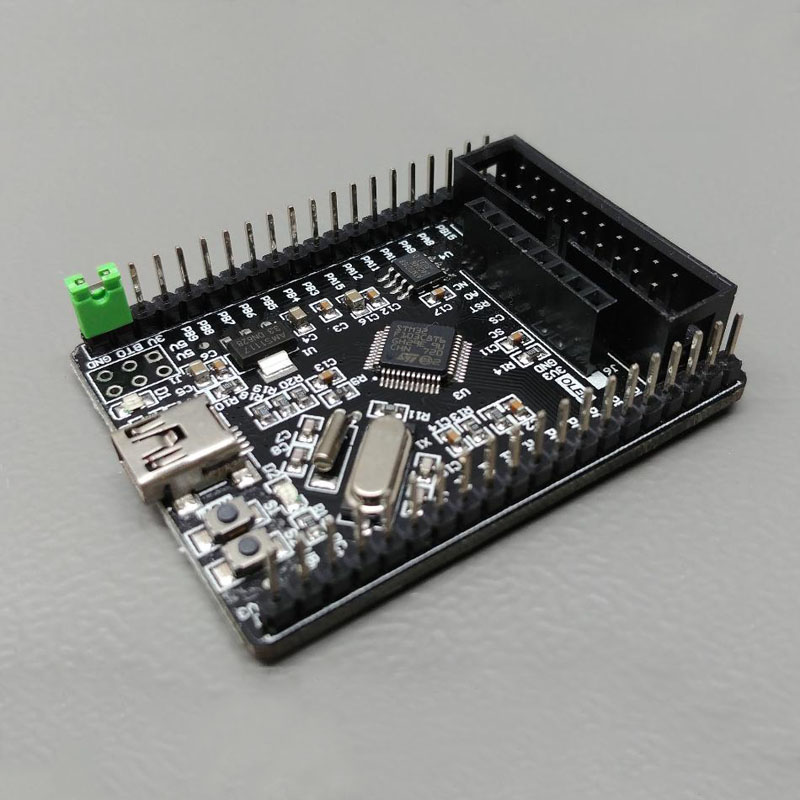

ARM STM32 MCU Board

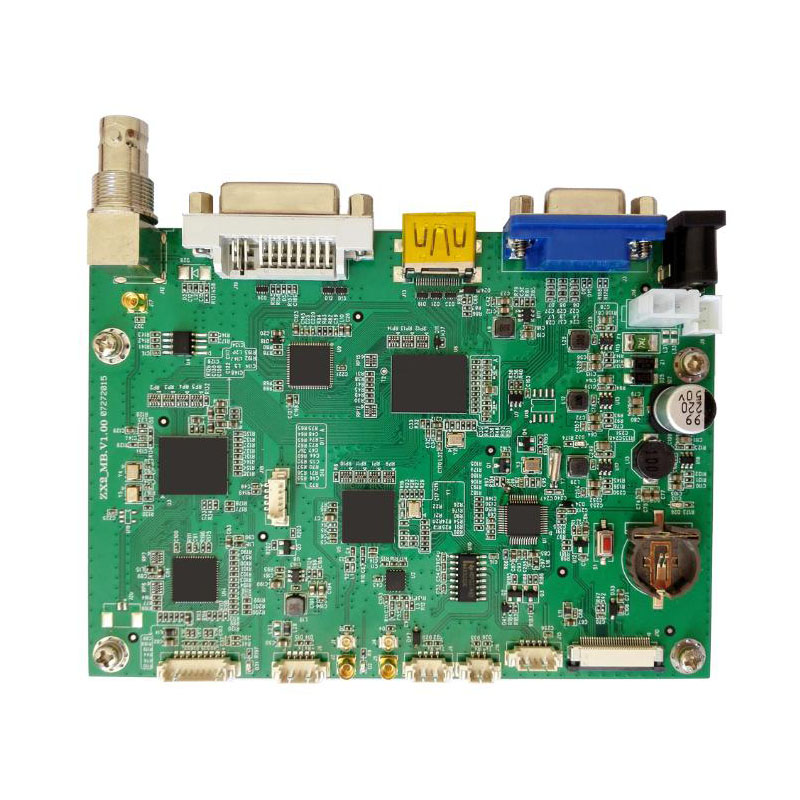

Ningbo Hi-tech Securus Electio Technologia Co., Ltd est summus tech societas quae operatur in consilio, progressu et productione ARM STM32 MCU Tabula. Fama societatis nostrae aedificatur ad fidem bonam et eximiam servitutem praebens, quae in diuturno collaborationibus consecuta est cum insignibus collegiis, regiminis institutionibus, et communitate usoris latis. Lorem in intelligentibus electronic imperium tabulas evolutionis, mechanicae et electricae ditionis producti designandi; single-chip microcomputer development, circuit design, et post-production experimentum. Consuetudinem consiliorum ambitum regere possumus ut tuis necessitatibus satisfaciamus, ut impletionem operis vestri intenti functionalities, sive expressa exigentias functionis sive ideam mere exhibeas.

Mitte Inquisitionem

YCTECH producti industriae imperium in tabula progressum includit industrialis imperium in tabula programmatis programmatis, upgrade programmatis schematici, consilium PCB, PCB productio et PCBA processus in Sinarum oram orientali sitae sunt. Societas nostra consilia, enucleat et opificiorum ARM STM32 MCU tabulas. Core: ARM32-bit Cortex-M3 CPU, summa frequentia operativa est 72MHz, 1.25DMIPS/MHz. Singulus cyclus multiplica et ferramenta divide.

Memoria: In-chip integratur 32-512KB Flash memoria. 6-64KB of SRAM memoria.

Horologium, reset ac potestas administratio: 2.0-3.6V potentia copia et intentione agentis ad I/O interface. Potestas-in reset (POR), potestas-down reset (PDR), et programmabilis voltage detector (PVD). 4-16MHz crystallus oscillator. Inaedificata in 8MHz RC ambitum oscillatoris ante officinam adaptatum. Internum 40 kHz RC ambitus oscillator. PLL pro CPU horologium. 32kHz crystallum cum calibratiis pro RTC.

Humilis potentia consummatio: 3 humilis potentia consummatio modi: somnus, siste, sto modus. VBAT AD POTESTATEM RTC ET RESCRIPTUM.

Debug modum: Vide debug (SWD) et interface JTAG.

DMA: 12-alveum DMA moderatoris. Subnixa periphericis: timers, ADC, DAC, SPI, IIC et UART.

Tres 12-bit us planities A/D convertentium (16 canales): A/D mensurae mensurae: 0-3.6V. Dual specimen et facultatem tenere. A temperatus sensorem in-chip integratur.

2-alveus 12-bit D/A converter: STM32F103xC, STM32F103xD, STM32F103xE exclusive.

Usque ad 112 velum I/O portus: Secundum exemplar, sunt 26, 37, 51, 80, et 112 portus I/O, quae omnes ad 16 vectores externos interrumpere possunt praevisi. Omnes autem inputationes analogorum accipere possunt inputationes usque ad 5V.

Usque ad 11 timetores: 4 16-bit timers, singuli cum 4 IC/OC/PWM vel calculis pulsus. Duae 16-bit 6-canales timers potestates progressae sunt: usque ad 6 canales pro PWM output adhiberi possunt. 2 vigil timers (dux vigil et fenestra vigil). Systick timer: 24-frenum considit. Duo 16-bit timers fundamentales DAC agitare solebant.

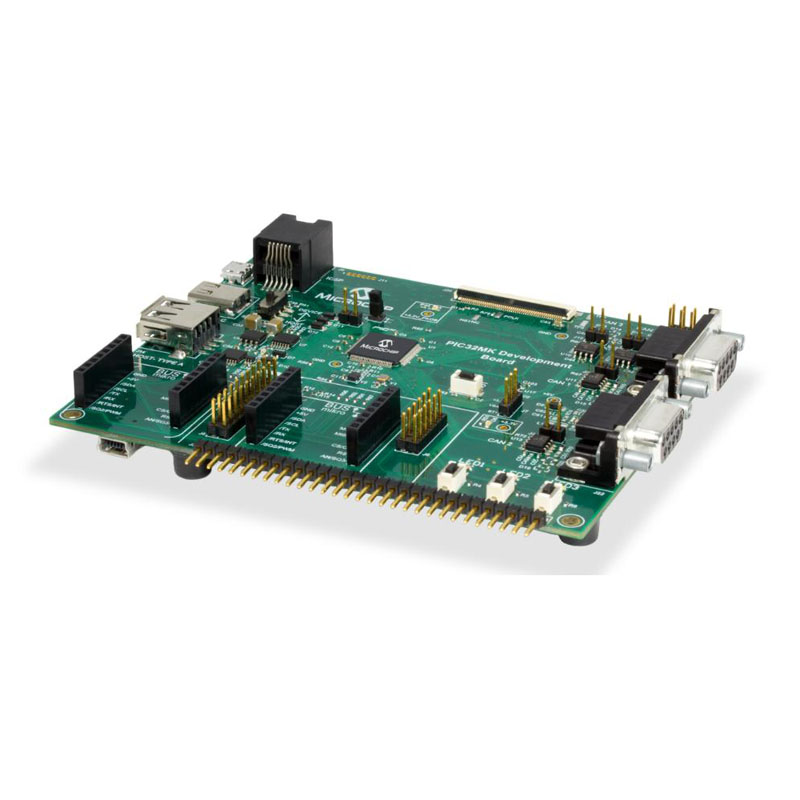

Usque ad 13 interfaces communicationis: 2 IIC interfaces (SMBus/PMBus). 5 interfaces USART (ISO7816 interface, LIN, IrDA compatible, debug imperium). 3 interfaces SPI (18 Mbit/s), quarum duae cum IIS multiplicantur. INTERFACERE POSSIT (2.0B). USB 2.0 interface pleno cursu. SDIO instrumenti.

Sarcina ECOPACK: STM32F103xx series microcontrolers involucrum ECOPACK capiunt.

ratio effectus

1. ARM Cortex-M3 nucleus insertus cum Mico infixa et SRAM memoria. Comparatus cum 8/16-bit machinis, ARM Cortex-M3 32-bit processor RISC efficientiam altiorem praebet codicem. STM32F103xx microcontrollers nucleum ARM immersum habent, ergo cum omnibus instrumentis ARM et programmatibus compatiuntur.

2. Mico Embedded memoria et RAM memoria: inaedificata usque ad 512KB Flash infixa, quae ad programmata et notitias reponendas adhiberi possunt. Usque ad 64KB of infixae SRAM legi et scribi possunt in cursu horologii CPU (statibus nulla mora).

3. Variabilis memoria stabilis (FSMC): FSMC infixa est in STM32F103xC, STM32F103xD, STM32F103xE, cum 4 chip electo, et quattuor modis sustentat: Flash, RAM, PSRAM, NOR et NAND. 3 FSMC interponunt lineae NVIC post OR coniunctae sunt. Nulla legitur FIFO scribere/nisi pro PCCARD, codicibus ex memoria externa exsequuntur, Booz non sustinetur, et scopus frequentiae SYSCLK/2 aequalis est, ergo cum horologii ratio 72MHz est, accessus externus exercetur in 36MHz.

4. Nested Vectored Interrupt Controller (NVIC): It can handle 43 maskable interrupt channels (excluding 16 interrupt lines of Cortex-M3), providing 16 interrupt priorities. Tightly coupled NVIC achieves lower interrupt processing latency, directly transfers the interrupt entry vector table address to the kernel, tightly coupled NVIC kernel interface, allows interrupts to be processed in advance, handles higher priority interrupts that arrive later, and supports tail Chain, automatically saves the processor state, and the interrupt entry is automatically restored when the interrupt exits, without instruction intervention.

5. Interpellare eventus moderatoris externi (EXTI): Interrumpat/eventus externus moderatoris ex 19 ore detectoris linearum ad interpellandum/eventum generandi petitiones consistit. Singulae lineae singillatim configurari possunt ut eventum felis eligere (ore ortu, ore cadente vel utraque) et singillatim palliata esse potest. Mandatum pendet ad statum obtinendum petitiones interrumpere. EXTI deprehendere potest cum pulsus in linea externa longior est quam periodus horologii interni APB2. Usque ad 112 GPIOs ad 16 lineas externas interrumpendas connexae sunt.

6. Horologium et initium: Adhuc necesse est ut horologium systematis incipientis, sed internus 8MHz crystallus oscillator seligatur sicut horologium CPU cum repositione. Horologium externum 4-16MHz seligi potest et ad effectum monitorem erit. Hoc tempore moderatorem interrumpentem ac programmatum interrumpentem administratio postea debilitata est. Eodem tempore interrumpere administrationem PLL horologii plene praesto est, si casus ferat (exempli gratia in casu obliqua oscillatoris crystallini adhibiti). Multiplex prae-comparator adhiberi potest frequentiam AHB ad configurandam, inclusam alta velocitate APB (PB2) et celeritas humilis APB (APB1). Summa frequentia rapidae APB est 72MHz, summa frequentia humilitatis APB est 36MHz.

7. Tabernus modus: In satus, paxillus Boot unum e tribus optionibus Tabernis eligere: importare ab usore Flash, importare ex systematis memoria, importare ex SRAM. Programma Boot importans in memoria systematis sita est et ad memoriam Flash per USART1 reprogramma adhibetur.

8. Potestas suppeditat schema: VDD, ambitus intentionis est 2.0V-3.6V, potentia externa per clavum VDD providetur, qui pro I/O et moderator internae intentionis adhibetur. VSSA et VDDA, extensionis 2.0-3.6V, externa analogia intentionis initus pro ADC, reset moduli, RC et PLL, intra ambitum VDD (ADC circumscribitur 2.4V), VSSA et VDDA coniungi debent cum VSS proinde. et VDD. VBAT, ambitus intentionis est 1.8-3.6V, cum VDD invalidus est, potestatem tribuit RTC, 32KHz crystalli oscillatoris et registri tergum (per potentiam mutandi percepi).

9. Potestas administratio: Fabrica plenam potestatem in reset (POR) et in circuitu reset (PDR) potestatem habet. Hic circuitus semper efficax est ut aliquae operationes necessariae peragantur cum ab 2V vel in 2V incipiendo. Cum VDD infra limitem specificum VPOR/PDR inferiorem est, machina quoque in repositione modo manere potest sine ambitu externo reset. In fabrica notas programmabiles voltage detectoris inhaerens (PVD). PVD in VDD deprehendere et comparare ad terminum VPVD adhibetur. Interrumpa generatur cum VDD minor est quam VPVD vel VDD maior quam VPVD. Ministerium exercitationis interrumpere potest nuntium monitionem vel MCU in statu tuto collocare. PVD a programmate est efficax.

10. Dispositio intentionis: Regulator voltage 3 modos operandi habet: principale (MR), consummatio potentiae humilis (LPR) et potestas descendit. MR in mode currens (modus currens) in sensu translaticio adhibetur, LPR in modo sistendi adhibetur, et potentia descendens adhibetur in stando modo: ordinator intentionis output est summus impedimentum, nucleus ambitus deprimitur, comprehendo. nulla consumptio (contenta tabularum et SRAM non interciderunt).

11. Low power consumption mode: STM32F103xx supports 3 low power consumption modes, so as to achieve the best balance between low power consumption, short startup time and available wake-up sources. Sleep mode: only the CPU stops working, all peripherals continue to run, wake up the CPU when an interrupt/event occurs; stop mode: allows to maintain the contents of SRAM and registers with minimal power consumption. The clocks in the 1.8V region are all stopped, the PLL, HSI and HSE RC oscillators are disabled, and the voltage regulator is placed in normal or low power mode. The device can be woken up from stop mode via an external interrupt line. The external interrupt source can be one of 16 external interrupt lines, PVD output or TRC warning. Standby mode: In pursuit of the least power consumption, the internal voltage regulator is turned off, so that the 1.8V area is powered off. PLL, HSI and HSE RC oscillators are also disabled. After entering standby mode, in addition to backup registers and standby circuits, the contents of SRAM and registers are also lost. The device exits standby mode when external reset (NRST pin), IWDG reset, rising edge on WKUP pin or TRC warning occurs. When entering stop mode or standby mode, TRC, IWDG and related clock sources will not be stopped.